# A 180nm CMOS Capacitorless Low Drop-Out Regulator for Battery-operated Systems

Jorge Pérez Bailón, Belén Calvo, Nicolás Medrano, Pedro A. Martínez

Afiliación: Grupo de Diseño Electrónico (GDE) Instituto de Investigación en Ingeniería de Aragón (I3A) Universidad de Zaragoza, Mariano Esquillor s/n, 50018, Zaragoza, Spain. Tel. +34-976762707, e-mail: <u>610686@unizar.es</u>

## **Abstract**

This paper presents a fully-integrated 180nm CMOS low drop-out regulator based on a simple telescopic cascode-compensated amplifier driving a PMOS pass-device. It provides a high precision 1.8V output voltage for battery voltages from 3.6V to 1.93V up to a 50mA load current with only  $22\mu A$  quiescent current.

## **Motivation**

The portable sensor market is pushing towards complete system-on-chip (SoC) solutions. One essential subsystem is the power management unit, where low drop-out (LDO) regulators play a key role delivering, under variations of load current IL and battery voltage VBAT, a stable power supply Vout. The goal of this work is the design of a LDO regulator to power both the read out and actuation electronics of a battery-compatible front-end sensor interface based on integrated analog lock-in amplifiers [1], with the aim to attain a forthcoming SoC CMOS system. The LDO specifications are fixed to: design in a low cost 0.18µm CMOS process with an output voltage of 1.8V from a 3.6V battery-compatible input voltage, maximum load current of 50mA and maximum 50pF load capacitor. Besides, it must comply with the two critical requirements of portable systems, i.e. reduced area and quiescent current, maintaining good regulating performance, stability and fast response times, a challenging task with an on-chip approach [2].

## Proposed LDO

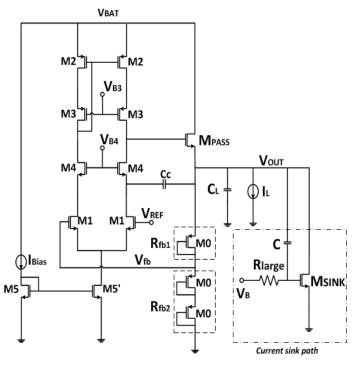

The proposed LDO is shown in Figure 1. The external  $V_{ref}$  is set to 1.2V, the size of the PMOS pass transistor  $M_{PASS}$  is  $(W/L)=(9.5 \text{mm}/0.34 \mu\text{m})$ , and the feedback resistances are  $R_{fb1}=60 k\Omega$ ,  $R_{fb2}=120 k\Omega$ , realized using identical diodeconnected PMOS to optimize area. To attain high precision regulation with minimum power

consumption, a single stage telescopic cascode error amplifier biased at  $10\mu A$  is used. Cascode compensation, using a single Cc capacitor is adopted, thus achieving higher speed and power supply rejection (PSR) compared to the commonly used Miller compensation. To enhance the transient behaviour, a very simple dynamically biased current sink path is added, which is only active when the load current varies from high to low, helping to discharge the path formed by  $(R_{fb1}+R_{fb2})$  and  $C_L$ .

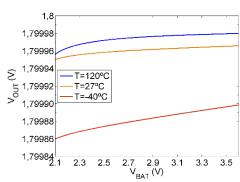

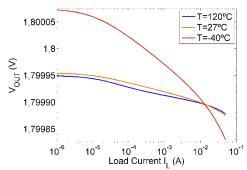

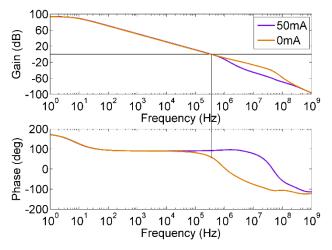

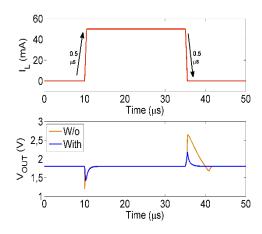

The LDO main performances are summarized on Table 1. It provides 1.8V output with 0.008% precision for input voltages  $V_{BAT}$ =1.93V-3.6V up to 50mA load current with a total quiescent current of 22 $\mu$ A. Line regulation is shown in Figure 2, for  $I_L$ =50mA (worst case); load regulation for  $V_{BAT}$ =2.1V (worst case) is shown in Figure 3. Figure 4 shows the open loop frequency performance with Cc=8.5pF to ensure PM>60° over all the operating conditions. Figure 5 shows the full load transient response, displaying the benefit of the current sink path.

### **Conclusions**

A high-performance fully-integrated LDO has been designed in 180nm CMOS. Compared to previous implementations with similar specifications [2-3], it attains a good trade-off between regulation performance, power, size and time response.

#### REFERENCES

- [1]. GARCIA-ROMEO, D., VALERO, M.R., MEDRANO, N., CALVO, B. and CELMA S. A High Performance LIA-Based Interface for Battery Powered Sensing Devices. *Sensors-Basel*, vol. 10, pp. 25260-25275, Sept. 2015.

- [2]. MILLIKEN, R.J., SILVA-MARTINEZ, J. and SANCHEZ-SINENCIO, E. Full On-Chip CMOS Low-Dropout Voltage Regulator. *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 54, no. 9, pp. 1879 1890, Sep. 2007.

- [3]. CHEN, C. and HUNG C.C. A fast self-reacting capacitor-less low-dropout regulator, *European Solid State Circuits Conference*, pp.375–378, 2011.

This work was supported in part by MINECO-FEDER (TEC2015-65750-R)

Figure 1: Schematic of the proposed CMOS LDO

Figure 2: Static Line regulation, I<sub>L</sub>=50mA

Figure 3: Static Load regulation,  $V_{BAT}$ =2.1V

Figure 4: Open-loop frequency response,  $V_{BAT}$ =2.1V

Figure 5: Full load transient w/o and with current sink path,  $V_{\rm BAT}$ =3.6V

Table 1: Comparison of CMOS capacitor-less LDO performances

| Parameter                    | This work, sim | [2], 2007, exp | [3], 2011, exp                 |

|------------------------------|----------------|----------------|--------------------------------|

| Technology (µm)              | 0.18           | 0.35           | 0.35                           |

| $V_{in}(V)$                  | 1.93 - 3.6     | 3              | 1.642 - 5                      |

| V <sub>out</sub> (V)         | 1.8            | 2.8            | 1.5                            |

| $V_{do}$ (mV)@ $I_{L,max}$   | 130@50mA       | 200@50mA       | 142@100mA                      |

| $I_q(\mu A)$                 | 22             | 65             | 27                             |

| $C_L(pF)$                    | 50             | 100            | 100                            |

| Line Regulation (mV/V)       | 0.0087         | ~23            | 1.046                          |

| Load Regulation (mV/mA)      | 0.0036         | ~0.56          | 0.0752                         |

| Full load settling time (μs) | 3              | 15             | 1 (I <sub>L</sub> :0 to 100mA) |

| PSR (dB)                     | -62@1kHz       | -57@1kHz       | 60.6@1kHz                      |