# A Fully Differential Variable Gain Amplifier for Portable Impedance Sensing Applications

Jorge Pérez-Bailón<sup>1</sup>, Jaime Ramírez-Angulo<sup>2</sup>, Belén Calvo<sup>1</sup>, Nicolás Medrano<sup>1</sup>

<sup>1</sup> Grupo de Diseño Electrónico (GDE)

Instituto de Investigación en Ingeniería de Aragón (I3A)

Universidad de Zaragoza, Mariano Esquillor s/n, 50018, Zaragoza, Spain.

Tel. +34-876553257, e-mail: <a href="mailto:jorgepb@unizar.es">jorgepb@unizar.es</a>

<sup>2</sup> Klipsch School of Electrical and Computer Engineering, New Mexico State University (Las Cruces, NM)

### **Abstract**

This paper presents a Variable Gain Amplifier (VGA) designed in a 0.18  $\mu m$  CMOS process to operate in an impedance sensing interface. Based on a transconductance-transimpedance (TC-TI) approach with intermediate analog-controlled current steering, it exhibits a gain ranging from 5 dB to 38 dB with a constant bandwidth around 318 kHz, a power consumption of 15.5  $\mu W$  at a 1.8 V supply and an active area of 0.021 mm<sup>2</sup>.

### **Motivation**

Electrical Impedance Spectroscopy (EIS), in which the electrical impedance of a sample under test is evaluated over a certain frequency span, is a powerful sensing technique in a broad range of areas including environmental monitoring, security enhancement, material characterization or the biomedical field [1]. However, despite its versatility, the explotation of these applications outside specialized laboratories is hindered by the lack of suitable fully integrated electronic interfaces complying with the critical low power and compact size requirements while simultaneusly preserving the accuracy and reliability of laboratory equipment.

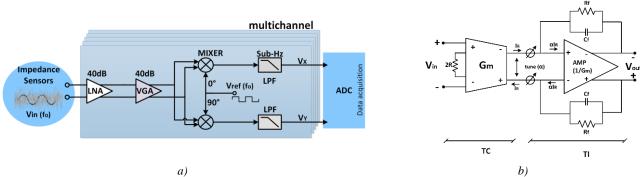

To extract the magnitude and phase, the simplest hardware-software technique, and thus potentially the most suitable for a CMOS low-voltage low-power (LVLP) implementation, is the Frequency Response Analyzer (EIS-FRA) technique based on quadrature modulators [2], shown in Fig. 1a. The analog prepocessing stage for a typical Mag-Phase read-out channel is a fixed (30 to 50 dB) gain Low Noise Amplifier (LNA) followed by a variable gain amplifier (VGA), which renders further adjustable amplification to optimize signal processing. This work focuses on the design of the VGA, being our design specifications: adjustable 40 dB gain, bandwith>100 kHz, to cover most EIS applications, and minimum size and power consumption.

This work has been partially supported by TEC2015-65750-R (MINECO/FEDER, UE)

## **Proposed structure**

The proposed VGA relies on a TC-TI approach (Fig. 1b) based on the topology presented in [3], but introducing a current steering technique in the transconductor output stage [4].

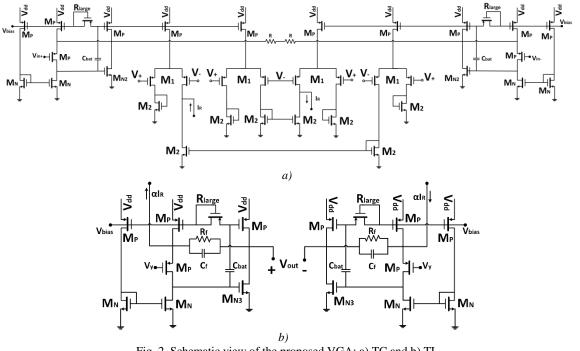

The transconductor (Fig. 2a) is a R-linear source degenerated differential pair, using super source follower input transistors which act as voltage buffers. Thus,  $V_{in}$  is driven to R terminals, generating the linear signal current  $I_{in}=(V_{in+}-V_{in-})/R$ , which is conveyed to the output stage through high-swing current mirrors that incorporate cascode current steering. In this way, the overall transconductor output current can be controlled through the cascode gate voltage, so  $G_m=\alpha/R$ , with  $0\leq\alpha\leq1$ .

The TI-stage (Fig. 2b), is made of two identical class-AB transresistance amplifiers set in a differential arrangement. Resistance  $R_{\rm f}$  yields the output voltage, being the overall gain given by  $A_V\!\!=\!\!\alpha R_{\rm f}/R$ , while  $C_{\rm f}$  is used for compensation. Both R and  $R_{\rm f}$  are linear passive elements, to optimize linearity and insensibilize the gain to PVT variations.

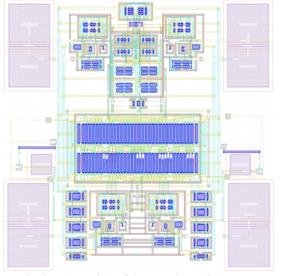

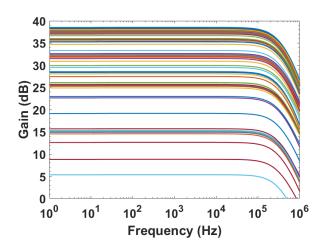

This VGA has been designed in the 0.18  $\mu m$  CMOS technology from TSMC, with a 1.8 V voltage supply and a bias current of 0.5  $\mu A$  using a class-AB topology to optimize power (achieved through a quasi floating  $C_{bat}$  and  $R_{large}$  gate). The layout is shown in Fig. 3. It provides a variable gain ranging from 5 dB to 38.5 dB (Fig. 4), preserving an almost constant bandwidth of 318 kHz. Total power consumption is 15.5  $\mu W$ , and active area is 0.021 mm<sup>2</sup>.

#### REFERENCES

- M. GROSSI et al. Electrical iimpedance spectroscopy (EIS) for biological analysis and food characterization: a review, *Journal of Sensors and Sensor Systems (JSSS)*, vol. 6, pp. 303-325, 2017.

- [2]. H. LI et al. CMOS Electrochemical Instrumentation for Biosensor Microsystems: A Review, *Sensors*, 2017.

- [3]. C. GARCIA-ALBERDI et al. Micropower Class-AB VGA With Gain-Independent Bandwidth, IEEE Trans. Circuits and Systems II: Exp. Briefs, vol. 60, pp. 397-401, 2013.

- [4]. J. PEREZ-BAILON et al. A 0.18µm CMOS Widely Tunable Low Pass Filter with sub-Hz Cutoff Frequencies, IEEE International Symposium on Circuits and Systems (ISCAS), 2018.

Fig. 1. Block diagram of: a) FRA-based impedance spectroscopy interface; and b) VGA proposed structure.

Fig. 2. Schematic view of the proposed VGA: a) TC and b) TI.

Fig. 3. Layout view of the complete VGA structure. Size: 144x145 µm<sup>2</sup>

Fig. 4. Gain variation over tuning.